International Advanced Research Journal in Science, Engineering and Technology

IARJSET

ISO 3297:2007 Certified

Vol. 3, Issue 7, July 2016

# Low-Power and Area-Efficient N-Bit Carry-Select Adder

K. Tejasvi<sup>1</sup>, G. Shyam Kishore<sup>2</sup>

M.Tech, PG Student, Jyothishmathi Institute of Technology and Science, Karimnagar<sup>1</sup>

Assoc. Prof in ECE Dept Jyothishmathi Institute of Technology and Science, Karimnagar<sup>2</sup>

Abstract: Design of High Efficiency Carry Select Adder Using SQRT Technique presents many opportunities for increasing the speed and reducing the area of any data processor. Only Carry Select Adder (CSLA) is the fastest adders which are used in many data-processing processors to perform fast arithmetic operation. From the structure of the CSLA, it is clear that there is scope for reducing the area and delay in the CSLA. In this thesis, we have implemented a carry select adder for the computational process, these modules are programmed in VHDL Carry Select Adder (CSLA) is the fastest adder in all other adder. This work uses very simple and efficient gate-level modification to reduce the area and delay of the CSLA. Based on this modification 8-, 16-, 32-bit square-root CSLA (SQRT CSLA) architecture has been developed and it is compared with the regular SQRT CSLA architecture. The proposed design has reduced area and delay as compared with the regular SQRT CSLA with only a slight reducing the delay. This work evaluates the performance of the proposed designs in parameters that is delay, area, and their products with logical effort. The results analysis shows that the proposed CSLA structure is better than the regular SQRT CSLA.

Keywords: Carry Save Adder, Carry Select Adder, Ripple Carry Adder, and Binary to Excess-1 Converter, Square root CSA, and VHDL.

# **I. INTRODUCTION**

In digital adders, the speed of addition is having the position in an adder is generated serially only after the limitation by the time required to propagate a carry previous bit position has been summed and a carry through the adder. Design of area and high-speed data path propagated into the next position. logic systems are one of the most important areas of research in VLSI system design. Addition widely the The CSLA is used in many calculation systems to avoid overall performance of digital systems and arithmetic the problem of carry propagation delay by independently function. In electronic system and applications adders are mostly used. Adders are used are multipliers, DSP to execute various algorithms like FFT, FIR and IIR.

Wherever concept of multiplication comes adders come in to the picture. As we know millions of instructions per second are performed in microprocessors. So, speed of operation is the most important constraint to be considered while designing multipliers. Due to device portability miniaturization of device should be high and power consumption should be low. Devices like Mobile, Laptops etc. require more battery backup. So, a VLSI designer has to optimize these three parameters in a design. These constraints are very difficult to achieve so depending on demand or application some compromise between constraints has to be made. Ripple carry adders exhibits the most compact design but the slowest in speed. Whereas carry look ahead is the fastest one but consumes more area. Carry select adders act as a compromise between the two adders. A carry-select adder can be implemented by using a single ripple-carry adder and an add-one circuit instead of using dual ripple-carry adders.

A multiplexer-based add-one circuit is proposed to reduce the area with less speed penalty. The sum for each bit

generating multiple carries and then select a carry to generate the sum. However, the CSLA is not area efficient because it uses multiple pairs of Ripple Carry Adders (RCA) to generate partial sum and carry by Considering carry input Cin=0 and Cin=1 then the final sum and carry are selected by the multiplexers.

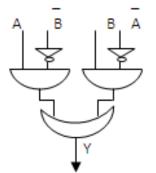

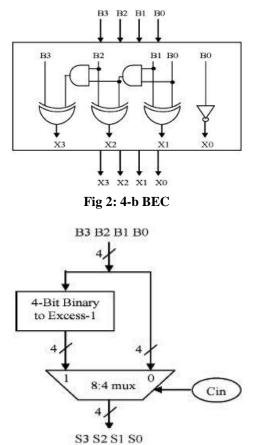

The basic idea of this work is to use Binary to Excess-1 Converter (BEC) instead of RCA with Cin=1 in the regular CSLA to achieve lower area and delay. The main advantage of this BEC logic comes from the lesser number of logic gates than the n-bit Full Adder (FA) structure.

Fig 1: Delay and area evalution of XOR

#### International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 7, July 2016

Fig3: 4-b BEC with 8:4 mux.

#### **II. CARRY SAVE ADDER**

A carry-save adder is one type of digital adder which is used in computer micro architecture for computational the sum of three or more n-bit numbers in binary. It is different from other digital adders in that it outputs two numbers of the same dimensions as the inputs, one which is a sequence of partial sum bits and another which is a sequence of carry bits. The carry-save unit consists of n full adders, each of which performs a single sum and carry bit based completely depends on the corresponding bits of the three input numbers.

Given the three n - bit numbers a, b, and c, it produces a partial sum Psi and a shift-carry Sci: sum can be performed by Shifting the carry sequence Sci left by one place, appending a 0 to the front (most significant bit) of the partial sum sequence Psi, Using a ripple carry adder to add these two together and produce the resulting n + 1-bit value. When adding together three or more numbers, using a carry-save adder followed by a ripple carry adder is faster than using two ripple carry adders. This is because a ripple carry adder cannot compute a sum bit without relatively slow, since each full adder must wait for the waiting for the previous carry bit to be produced, and thus carry bit to be calculated from the previous full adder. The has a delay equal to that of n full adders. A carry-save gate delay can easily be calculated by inspection of the full adder, however, produces all of its output values in parallel, and thus has the same delay as a single full-adder. Thus the total computation time (in units of full-adder the critical path (worst case) delay is 31 \* 2(for carry delay time) for a carry-save adder plus a ripple carry adder propagation) + 3(for sum) = 66 gate delays However, the

is n + 1, whereas for two ripple carry adders it would be 2n.

#### **III. CARRY SELECT ADDER USING RIPPLE CARRY ADDER**

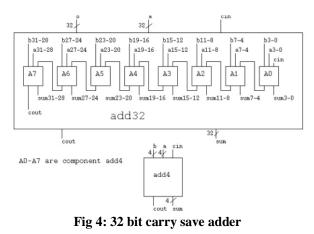

Arithmetic operations like addition, subtraction, multiplication, division are basic operations to be implemented in digital computers using basic gates like AND, OR, NOR, NAND etc. Among all the arithmetic operations if we can implement addition then it is easy to perform multiplication, subtraction or division .Half Adders can be used to add two one bit binary numbers. It is also possible to create a logical circuit using multiple full adders to add N-bit binary numbers. Each full adder inputs Cin which is the Cout of the previous adder. This kind of adder is a Ripple Carry Adder, since each carry bit "ripples" to the next full adder. The first full adder may be replaced by a half adder. The block diagram of 16-bit Ripple Carry Adder is shown here below32 Bit Carry Select Adder With Bec-1

CSLA F is a Full Adder.

The structure of ripple carry adder is simple, which allows for fast design time; however, the ripple carry adder is adder circuit. Each full adder requires three levels of logic. In a 32-bit [ripple carry] adder, there are 32 full adders, so

International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 7, July 2016

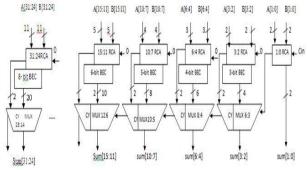

Ripple Carry Adders (RCA) to generate partial sum and it is verified that there is large reduction in number of carry by considering carry input Cin=0 and Cin=1 then the gates. The MUX is used to select either the BEC output or final sum and carry are selected by the multiplexers The the inputs given directly to a BEC circuit .In this design, structure of the 32-b SQRT CSLA using RCA is 32 Bit the major function of MUX is to derive the adder speed. Carry Select Adder With Bec-1 shown in Fig. It has five groups of different size RCA.

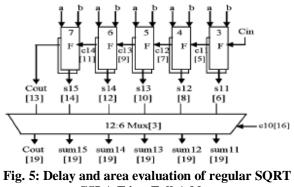

The delay and area evaluation of each group are shown in Fig. in which the numerals within specify the delay values, e.g., sum2 requires 10 gate delays The steps leading to the evaluation are as\ follows. 1) The group2 has two sets of 2-b RCA. Based on the consideration of delay values of the arrival time of selection input of 6:3 mux is earlier than and later than. Thus, is summation of and 2) Except for group2, the arrival time of mux selection input is always greater than the arrival time of data outputs from the by using 32-bit SQRT CSLA as compared to 32-bit CSLA RCA's. Thus, the delay of group3 to group5 is determined, using RCA. respectively as follows: 3) the one set of 2-b RCA in group2 has 2 FA for and the other set has 1 FA and 1 HA for. Based on the area count, the total number of gate counts in group2 is determined. For the remaining group's by using 32-bit SQRT CSLA as compared to 32-bit CSLA the arrival time of mux selection input is always greater using RCA. The comparative values of areas shows that than the arrival time of data inputs from the BEC's. Thus, the number of LUT will be more for modified method for the delay of the remaining groups depends on the arrival the 32-bit. time of mux selection input and the mux delay.

# **IV. CARRY SELECT ADDER USING BEC-1**

This structure is similar to regular 32-bit SQRT CSLA, the only change is that, we replace RCA with Cin=1 among the two available RCAs in a group with a BEC. This BEC can perform the similar operation as that of the replaced RCA with Cin=1.Fig shows the modified diagram 16-bit After simulation the different size codes are synthesized SQRT CSLA. The number of bits required for BEC logic using Xilinx ISE13.2i, Simulated files are imported into is 1 bit more than the RCA bits. The modified block the synthesized tool and values of delay and area are diagram is also divided into various groups of variable noted. sizes of bits with each group having the ripple carry adders, BEC and mux. First group contain one RCA which is having input of lower significant bit and carry in bit and produces result of sum (1:0) and carry out which is acting as mux selection line for the next group. The XOR gate in BEC of Modified CSLA is replaced with the optimized XOR gate in AOI of Modified Area Efficient CSLA .With BEC there is reduction of gates by replacing n bit RCA with n+1 bit BEC.

Fig 6: 32 bit Carry Select Adder using RCA AND bec-1

CSLA is not area efficient because it uses multiple pairs of When the optimized XOR gate is used in Modified CSLA,

#### V. DELAY, AREA EVALUATION METHODOLOGY **OF CSA, CSLA USING RIPPLE CARRY ADDER** AND CSLA USING BEC-1

Delay and area evaluation methodology of CSA, CSLA using ripple carry adder and csla using BEC-1 is shown in below table. In 32-bit CSA the area is increased as compared to regular csla and modified CSLA modified CSLA. In 32-bit SQRT CSLA moderate area is required as compared to CSA and CSLA using RCA. Delay is reduced

The n 32-bit SQRT CSLA moderate area is required as compared to CSA and CSLA using RCA. Delay is reduced

# VI. RESULTS

The implemented Design of 32 bit SQRT CSLA has been simulated using VHDL. The 32-bit CSLA adder are designed and simulated using VHDL and the results are compared with CSA and Carry Select Adder using RCA.

#### **VII. CONCLUSION**

This paper proposed a simple approach to reduce area and delay of SORT CSLA using BEC-1 architecture. The RCA with BEC in the structure is a great advantage to reduction in the number of gates and LUTs.

The result as shown in comparison table states that the modified 32-bit SQRT CSLA has a slightly large area for lower order bit which reduces for higher order bit and also delay is reduced to a great extent.

Thus the result shows that using modified method the area and delay will decrease so it is a good alternative for adder implementation in many data processors. Comparison table states that the modified 32-bitSQRT CSLA has a slightly large area for lower order bit which reduces for higher order bit and also delay is reduced to a great extent. Thus the result shows that using modified method the area and delay will decrease so it is a good alternative for adder implementation in many data processors.

# **IARJSET**

International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 7, July 2016

# ACKNOWLEDGEMENT

Many people have contributed in bringing this report to its present form. I am Ms. K. Tejasvi ascribe my success in this venture to my guide shyamkishore of Electronics and Communication Department, Jyothishmathi college of Engineering and Technology, Karimnagar. He endeavor for perfection, indefatigable Zeal, enthusiasm, foresight and innovation contributed in a big way in completing this report with considerable ease in the stipulated time. I am also grateful to **Dr. Ravikiran**, H.O.D. of Electronics and Communication Department, jits, karimnagar.

#### REFERENCES

- Kuldeep Rawat, Tarek Darwish. and Magdy Bayoumi, March 2002 45th Midwest Symposium on Circuits and Systems, vol.1, pp. 467-470, "A low power and reduced area Carry Select Adder".

- [2] O. J. Bedrij, June1962, IRE transactions on Electronics Computers, vol.EC-11, pp. 340-346 "Carry-Select Adder".

- [3] O. J. Bedrij, "Carry-select adder," IRE Trans. Electron. Comput., vol. EC-11, no. 3, pp. 340–344, Jun. 1962.

- [4] B.Ramkumar, Harish M Kittur and P.Mahesh Kannan, European Journal of Scientific Research, vol.42, pp.53-58, 2010, "ASIC implementation of Modified Faster Carry Save Adder".

- [5] J. M. Rabaey, New Jersey, Prentice-Hall, "Digital Integrated Circuits- A Design Perspective", 2001.

- [6] M.Moris Mano, Pearson Education, 3rd edition, "Digital Design" 2002.

- [7] T.-Y. Chang and M.-J. Hsiao Electronics letters, vol.34, pp.2101-2103,"Carry-Select Adder using single Ripple-Carry Adder",October 1998.

- [8] Youngjoon Kim and Lee-Sup Kim,IEEE International Symposium on Circuits and Systems, vol.4, pp.218-221, "A low power carry select adder with reduced area" May 2001.

- [9] Behnam Amelifard, Farzan Fallah and Massoud Pedram, Sixth International Symposium on Quality of Electronic Design, pp.148-152"Closing the gap between Carry Select Adder and Ripple Carry Adder: a new class of low-power high-performance adders". April 2005.

- [10] Akhilesh Tyagi, IEEE International Conference on Computer design, pp.255-258, "A Reduced Area Scheme for Carry-Select Adders", Sept 1990

- [11] D. J. Kinniment, IEEE transaction on very large scale integration (VLSI) systems, vol.4, pp.137-140, "An evaluation of asynchronous addition", March 1996.

- [12] Richard P. Brent and H. T. Kung, IEEE transactions on Computers, vol.c-31, pp.260-264, "A Regular Layout for Parallel Adders", March 1982.

- [13] O. J. Bedrij, "Carry-select adder," IRE Trans. Electron. Comput., vol. EC-11, no. 3, pp. 340–344, Jun. 1962.

- [14] Y. Kim and L.-S. Kim, "64-bit carry-select adder with reduced area," Electron. Lett., vol. 37, no. 10, pp. 614–615, May 2001.

- [15] Y. He, C. H. Chang, and J. Gu, "An area-efficient 64-bit square root carryselect adder for low power application," in Proc. IEEE Int. Symp. Circuits Syst., 2005, vol. 4, pp. 4082–4085.

- [16] B. Ramkumar and H.M. Kittur, "Low-power and area-efficient carry-select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–375, Feb. 2012.

- [17] I.-C. Wey, C.-C. Ho, Y.-S. Lin, and C. C. Peng, "An area-efficient carry select adder design by sharing the common Boolean logic term," in Proc. IMECS, 2012, pp. 1–4.

- [18] S.Manju and V. Sornagopal, "An efficient SQRT architecture of carry select adder design by common Boolean logic," in Proc. VLSI ICEVENT, 2013, pp. 1–5.

- [19] B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs, 2nd ed. New York, NY, USA: Oxford Univ. Press, 2010.

# BIOGRAPHIES

**K. Tejasvi** received B. Tech (ECE) degree in 2014 from BITSW, Mangalpally, Ranga Reddy (Dist), pursuing my M.Tech in JITS, Karimnagar, branch DSCE.

**G. Shyam Kishore** received his B.Tech (ECE) degree in 2003 from MTEC, Peddapalli. And received his M.Tech (VLSI) degree in 2009 from JBIET, Hyderabad. Currently, he is working as Assoc. Prof in ECE Dept, JITS, Karimnagar with 13 years of teaching

experience.